發布日期:2024-11-08 浏覽次數:

供稿:凝聚态物理與材料物理研究所 |

編校:時暢 |

編輯:陳偉華 |

審核:楊學林

近日,beat365官方网站凝聚态物理與材料物理研究所、納光電子前沿科學中心、人工微結構和介觀物理國家重點實驗室葉堉課題組與合作者提出了一種共濺射摻雜技術,在二維半導體碲化钼薄膜中實現精準地空穴導電(p型)或電子導電(n型)的二維半導體摻雜技術。此外,共濺射摻雜技術可在碲化钼薄膜中進行空間區域的選擇性摻雜,将p型和n型的碲化钼薄膜集成在單一基底上。利用上述技術,成功制造出芯片尺寸的二維互補型反相器電路陣列,該電路具有出色的器件性能和良率,展示了二維半導體材料在大規模集成電路中的應用潛力。2024年11月7日,相關研究成果以“用于單片集成電路的二維半導體精準p型和n型摻雜技術”(Precisep-type andn-type doping of two-dimensional semiconductors for monolithic integrated circuits)為題發表于《自然·通訊》(Nature Communications)上。

摻雜技術是現代集成電路産業的基礎,是指在半導體材料中人工摻入一定量的特定雜質原子,以改變半導體材料的電學性能,由此可以制造出各種功能型電子器件和電路。例如半導體矽,可以在熔融過程之前添加諸如磷或硼之類的摻雜劑,随後通過提拉法生産具有不同導電性類型和導電能力的摻雜單晶矽晶圓片。此外,離子注入是矽基集成電路的一項基本技術,可以選擇性摻雜特定區域以構築p型區和n型區,進而制造互補型集成電路芯片。二維原子晶體,由于其原子厚度和堆疊能力,已經成為推進摩爾定律的候選材料之一,特别是在晶體管縮放和層間互連方面。然而,上述摻雜技術在二維半導體材料中進展緩慢,主要原因是很難在合成過程中精準微量的進行雜質原子摻入,并且像離子注入這樣的傳統工藝對原子級厚度的二維原子晶體無法實現有效的空間選擇性摻雜。

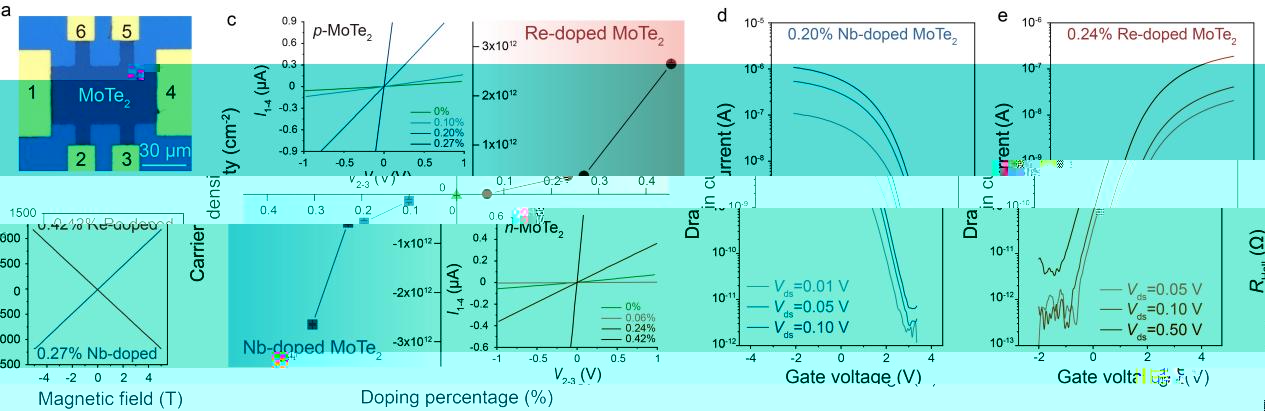

基于上述研究背景,葉堉課題組與合作者在前期二維碲化钼薄膜相變與可控制備的基礎上,提出二維半導體碲化钼(MoTe2)薄膜的共濺射摻雜技術。利用雙靶位共濺射方式,在高溫碲化之前向钼膜中精準控制摻入一定量的雜質元素铌(用于空穴摻雜)或铼(用于電子摻雜)。然後,通過化學氣相沉積(CVD)碲化Mo膜前驅體從而獲得摻雜的少層MoTe2膜(圖1 a)。利用該方法可以制備大面積、晶圓尺寸的摻雜二維半導體MoTe2薄膜(圖1 b),展示其大規模應用的潛力。與此同時,對摻雜後的二維MoTe2薄膜進行掃描隧道顯微鏡微分電導譜(STS)表征(圖1 c)。通過STS表征結果可清晰觀察到MoTe2半導體随着摻雜元素的改變,其費米能級(EF)位置明顯移動。對于铌(Nb)摻雜的情況,EF更接近價帶頂,表現出p型半導體特征。而铼(Re)元素的摻雜結果則相反,其費米能級更靠近導帶底。考慮到樣品之間的唯一區别是在Mo膜前驅體中引入了不同的雜質原子,并且它們是在相同的條件下制備和測量的,因此可以排除分子吸附或環境因素對費米能級位置的影響。STS的表征結果直觀地展現出摻雜劑對二維半導體MoTe2的費米能級位置的影響,随後研究人員對摻雜的MoTe2半導體進行電學特性的表征分析。

圖1.利用共濺射摻雜技術制備晶圓級摻雜二維碲化钼薄膜,并用掃描隧道顯微鏡譜對其半導體能帶結構進行表征分析。

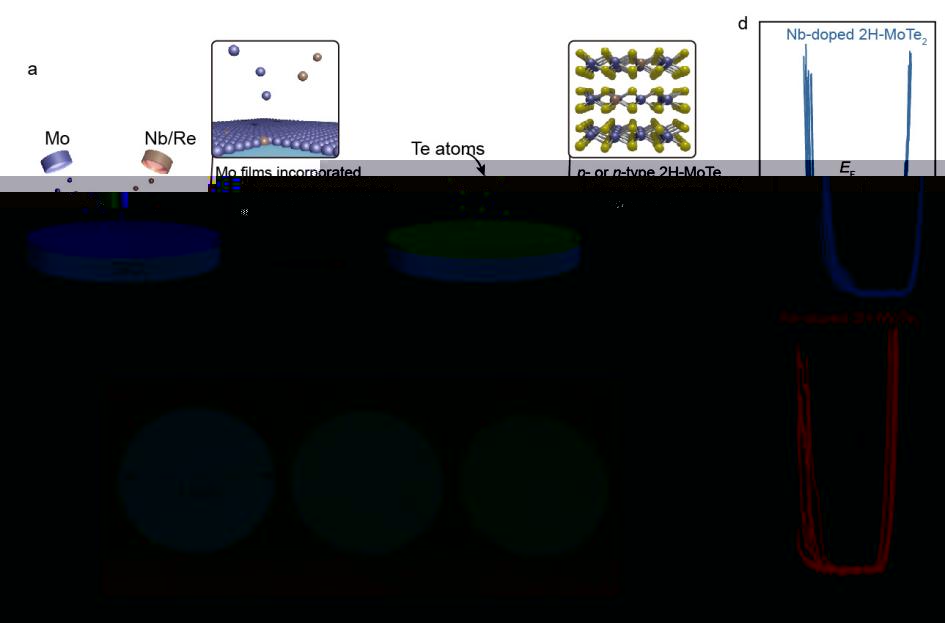

在确定Nb和Re摻雜劑對二維半導體MoTe2的有效p型和n型摻雜後,必須考慮的是實現可控的精準摻雜,特别是摻雜過程中産生的載流子濃度的表征。為了控制Mo薄膜中摻雜的比例,合作團隊在共濺射過程中保持Mo的沉積速率恒定的情況下,同時對摻雜劑(Nb或Re)的沉積速率進行微調,實現了微量摻雜Nb(0.10%)和Re(0.06%)。随後,通過CVD生長獲得了不同載流子類型和載流子濃度的MoTe2薄膜。為不同的樣品制作霍爾器件以表征其載流子類型和濃度(圖2 a)。Nb和Re摻雜樣品的霍爾電阻測量顯示出相反的極性,進一步證實了Nb(Re)摻雜分别在MoTe2薄膜中引入了空穴(電子)載流子。通過計算霍爾電阻随磁場變化曲線斜率的倒數來确定載流子濃度。未人工摻雜的MoTe2顯示出較低的空穴載流子濃度(2.66×1010cm−2)。在加入微量摻雜劑Re(0.06%)後,對空穴載流子進行補償,将樣品轉化為電子濃度為3.94×109cm−2的導電材料。之後,進一步提高雜質靶材的濺射功率,電子濃度随Re摻雜量的增加而增加。同樣,随着Nb摻雜量的增加,樣品中的空穴濃度也随之增加。随着p型和n型雜質載流子濃度的增加,摻雜MoTe2薄膜的電導率逐漸增加,這可以從四探針電流-電壓曲線中得到證明(圖2 c的插圖)。對适當摻雜濃度的MoTe2薄膜進行場效應晶體管器件制備和電學測試,器件的轉移特性曲線可觀察到明顯的p型和n型溝道特征,開關比約為105。成功制備的可控制摻雜類型和載流子濃度的二維半導體MoTe2薄膜,具有實際的電子器件應用潛力。

圖2.對摻雜的二維半導體碲化钼薄膜進行霍爾電學表征和晶體管性能測試。

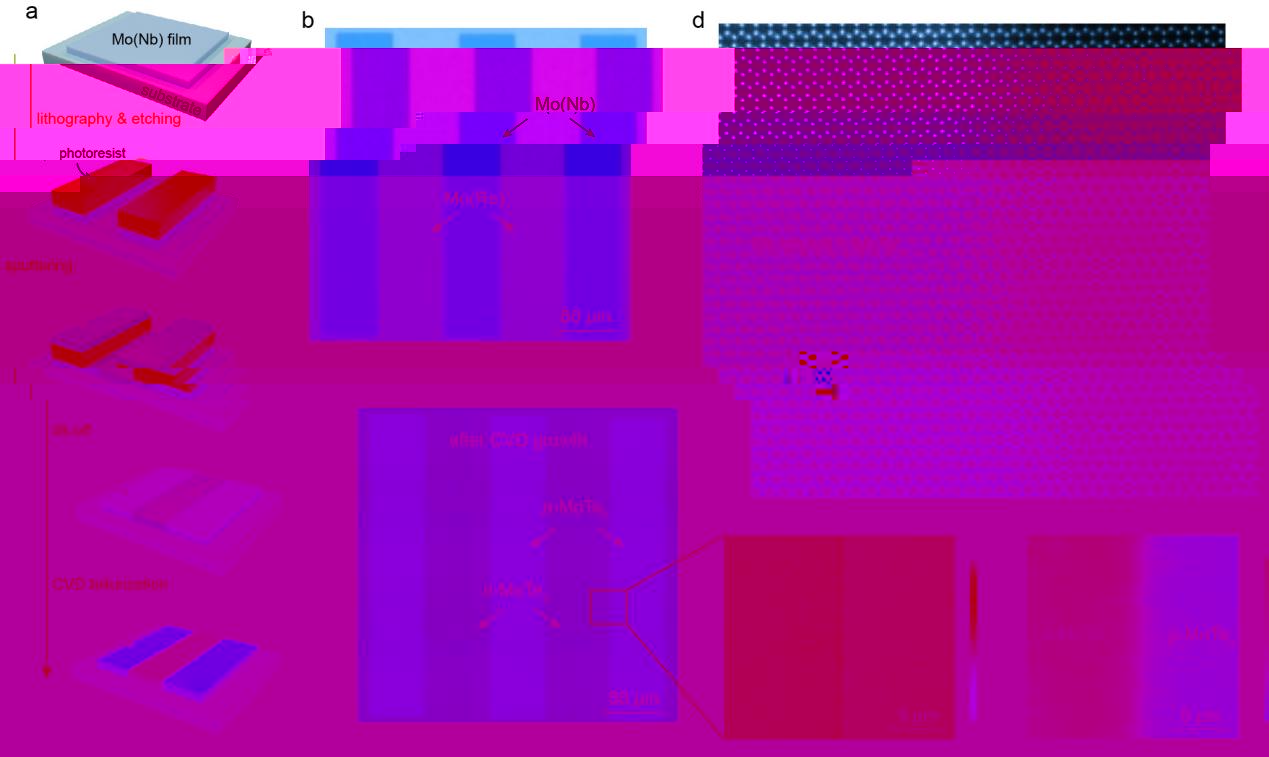

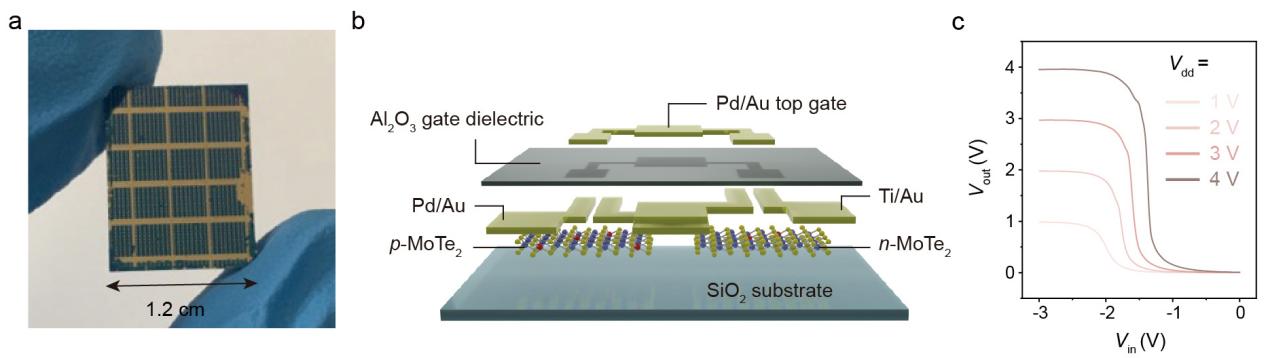

對半導體材料空間區域選擇性摻雜是實現集成電路的關鍵步驟。基于已開發的共濺射摻雜技術和MoTe2薄膜“固-固”相變過程,我們設計了一步生長方法來獲得二維半導體MoTe2薄膜的圖案化摻雜結構。首先,在襯底上沉積Nb摻雜的Mo膜,然後使用傳統的光刻和物理蝕刻技術進行圖案化(圖3 a)。随後,沉積Re摻雜的Mo膜,在去膠過程之後,獲得包含Nb和Re摻雜區域的連續圖案化前驅體Mo膜(圖3 b)。采用一步CVD生長方法合成了平面集成的p型和n型圖案化MoTe2薄膜(圖3 c)。在相變和再結晶過程中,單晶MoTe2晶疇延伸到不同摻雜區域的界面上,形成了具有p型和n型圖案化區域的單晶MoTe2薄膜。高角度環形暗場掃描透射電子顯微鏡(HAADF-STEM)圖像顯示Nb摻雜和Re摻雜區域之間的界面有一個完美的晶格,沒有任何晶向角度偏轉和晶界(圖3 d)。利用開爾文探針原子力顯微鏡(KPFM)測量界面表面電勢差,驗證了摻雜誘導費米能級位移的有效性。與Nb摻雜的MoTe2相比,Re摻雜的MoTe2區域表現出明顯更高的表面電勢(圖3 f),符合預期的摻雜特性。利用空間區域的選擇性摻雜技術,合作團隊制備了大面積p-MoTe2和n-MoTe2單片集成的二維材料反相器電路陣列(圖4 a和b)。當驅動電壓Vdd=4 V時,反相器電路增益達到38,功耗89 nW。綜上所述,研究人員提出一種有效、可控的二維半導體精準摻雜技術,有利于促進二維半導體材料在單片集成互補型電路領域中的應用。

圖3.對二維半導體碲化钼薄膜進行共濺射空間區域選擇性摻雜及其掃描透射電子顯微鏡(STEM)和開爾文探針原子力顯微鏡(KPFM)表征分析。

圖4.大面積制備基于二維摻雜碲化钼半導體的互補型反相器電路陣列及其性能測試。

beat365官方网站博雅博士後潘宇為該工作第一作者;武漢大學何軍教授和張晨棟教授、北京理工大學徐曉龍預聘教授、beat365官方网站葉堉研究員為共同通訊作者,主要合作者還包括beat365官方网站高鵬教授。

上述研究工作得到國家重點研發計劃、國家自然科學基金、北京市自然科學基金、beat365長三角光電科學,以及人工微結構和介觀物理國家重點實驗室等支持。

論文原文鍊接:https://www.nature.com/articles/s41467-024-54050-2.pdf